(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 11, November 2015

# Single phase Multilevel Inverter using Coupled Inductors

Merina David<sup>1</sup>, Muhamed Noufal C<sup>2</sup>

PG Student [PEPS], Dept. of EEE, Federal Institute of Science and Technology, Angamaly, Kerala, India<sup>1</sup>

Assistant Professor, Dept. of EEE, Federal Institute of Science and Technology, Angamaly, Kerala, India<sup>2</sup>

**ABSTRACT**: Multilevel inverters have been attracting in favor of academia as well as industry in the recent decade for high-power and medium-voltage energy control. In addition, they can synthesize switched waveforms with lower levels of harmonic distortion than an equivalently rated two-level inverter. Multilevel converters have received increased interest recently as a result of their ability to generate high quality output waveforms with a low switching frequency. The multilevel concept is used to decrease the harmonic distortion in the output waveform without decreasing the inverter power output. In this work a new class of multilevel inverter with coupled inductor was introduced. No split of the dc voltage capacitor is needed, totally avoiding the voltage balancing problem in conventional multilevel inverters. This inverter is based on the widely used three-arm power module making it very easy to construct. Simulation and experimental results show the validity of this inverter.

KEYWORDS: Multilevel, Coupled inductor, Harmonics, Turns ratio

### **I.INTRODUCTION**

The birth of semiconductor technology and its widespread acceptance and applications fuelled the design of various power converter topologies. Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a multilevel power inverter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel inverter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, and fuel cells can be easily interfaced to a multilevel inverter system for a high power application.

For single-phase multilevel inverters, the most common topologies are the cascaded, diode-clamped, and capacitor clamped types [2]. In general, multilevel inverter topologies can be classified into two types: Type I and Type II. Type I uses multiple dc voltage sources and Type II uses multiple (split or clamping) dc voltage capacitors. Type I includes the traditional cascaded topologies. Type II includes the conventional diode-clamped, capacitor-clamped inverters. In terms of single phase multilevel inverters, the disadvantages of the two types are apparent. Type I suffers from the availability of the multiple dc voltage sources. Apart from the conventional multilevel inverters, many more circuit configurations have been designed and implemented. The necessity if such topologies were to reduce the number of components in the configuration and also to reduce the control complexities. Arrival of new topologies resulted in reduced complexity of voltage balancing, less switching losses.

A multilevel inverter with only one dc source and no split capacitors may be the most desirable topology but unfortunately this type of inverter has yet to be discovered. A new topology of multilevel inverter with coupled inductors is attractive in this context. The importance of this innovation lies within using minimum number of elements and PE switches, while increasing number of voltage levels.

### **II.CONVENTIONAL FIVE LEVEL INVERTER**

The conventional inverter with coupled inductor is the five level inverter. The topology is the three arm power module consisting of a single DC source, six power electronics switches and a pair of coupled inductors. The numbers of turns in the coupled inductor are same or the turns ratio is1:1. The switches in a leg are switched in a complementary fashion. Two of the switches are switched in the fundamental frequency. Whereas other

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 11, November 2015

six are switched in high frequency. The coupled inductors will perform as an adder of the two input voltage at the non common-connected terminals with the common-connected terminal as the output. Actually, without the help of the coupled inductors, the proposed inverter will not be able to output five-level voltage. The switching stresses on all the switches are same and are equal to half the DC link voltage. The topology consists of less number of switches when compared to the conventional multilevel inverter.

## **III.MODIFIED SEVEN LEVEL INVERTER**

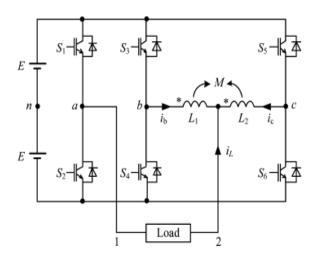

In the conventional five level inverter there are redundant switching states. The redundancy is because the coupled inductors are having equal no of turns. If the turns ratio is changed to 1:2 ratio we can increase the number of levels. Thus the modified seven level inverter have the same power circuit as shown in Fig1.The DC link voltage is 2E.The seven levels of the inverter are+2E,+4E/3,+2E/3,0,-2E/3 -2E/3,-2E.

Fig.1 Modified Seven level inverter.

## A. ROLE OF THE COUPLED INDUCTORS

It is, in fact, the adoption of the coupled inductors that makes it possible to output seven level voltages with only one DC voltage source. So the role of the coupled inductors will be analysed first. Assuming  $N_2/N_1$ =a, then  $L_1$ =L,  $L_2$ =a<sup>2</sup>L, M=aL. The voltage equations are shown below.

$$V_{bn} = L \frac{di_b}{dt} - aL \frac{di_c}{dt} \tag{1}$$

$$V_{cn} = a^2 L \frac{di_c}{dt} - a L \frac{di_b}{dt}$$

(2)

Solving the above equations we get

$$V_{2n} = \frac{aV_{bn} + V_{cn}}{1+a}$$

(3)

Therefore,  $V_{2n}$  is the weighted average of  $V_b$  and  $V_c$ . Assuming turns ratio equals to 2,  $V_n$  is calculated from the following equation.

$$V_n = \frac{V_{bn} + 2V_{cn}}{3} \tag{4}$$

Thus the switching states of the inverter can be summarized by Table 1

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 11, November 2015

## B. Design of the coupled inductors

According to (3) and (4), Currents of coupled inductors in can be written down as following equations

$$V_{an} - V_{bn} = 4L \frac{di_b}{dt} - \frac{di_c}{dt}$$

(5)

$$4i_b - i_c = \int \frac{V_{ab}}{L} = i_{ripple} \qquad (6)$$

$$i_b = 0.2(i_l + i_{ripple}) \tag{7}$$

$$i_c = 0.8(i_l + i_{ripple})$$

(8)

| S1 | S2 | <b>S</b> 3 | <b>S</b> 4 | S5 | <b>S</b> 6 | $V_{ab}$ |

|----|----|------------|------------|----|------------|----------|

| 1  | 0  | 0          | 1          | 0  | 1          | +2E      |

| 1  | 0  | 0          | 1          | 1  | 0          | +4E/3    |

| 1  | 0  | 1          | 0          | 0  | 1          | +2E/3    |

| 1  | 0  | 1          | 0          | 1  | 0          | 0        |

| 0  | 1  | 0          | 1          | 0  | 1          | 0        |

| 0  | 1  | 0          | 1          | 1  | 0          | -2E/3    |

| 0  | 1  | 1          | 0          | 0  | 1          | -4E/3    |

| 0  | 1  | 1          | 0          | 1  | 0          | -2E      |

Table 1 Switching states of seven level inverter

### **B.MODULATION METHOD**

The switching state of S1 is decided by the sign of  $V_{12ref}$  (the reference of V12). S1 is 1 if  $V_{12ref}$  0 and S1 is 0 if  $V_{12ref}$  0.S2 is the complement of S1.Thus we can see that both S1and S2 is switched at fundamental frequency and it is very easy to implement. By analyzing the states we can see that the rest of the switches are switched in high frequency. To decide the switching states of (S3, S5), the following cases will be discussed:

- $V_{12ref}$  is between 0 and +2E/3, then switching states are (1, 0).

- $V_{12ref}$  is between +2E/3 and +4E/3, then switching states are (0, 1).

- $V_{12ref}$  is between +4E/3and +2E, then switching states are (0,0)

- $V_{12ref}$  is between 0 and -2E/3, then switching states are (0,1)

- $V_{12ref}$  is between -4E/3 and -2E, then switching states are (1,0)

- $V_{12ref}$  is between -4E/3and -2E, then switching states are (1,1).

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 11, November 2015

Table 2 shows the components required for a seven level inverter employing different topology, it is evident from the tables that components required is less for the topology

|                              | Diode clamped<br>inverter | Capacitor<br>clamped | Cascaded<br>Inverter | Modified<br>inverter |

|------------------------------|---------------------------|----------------------|----------------------|----------------------|

| Switches                     | 12                        | 12                   | 12                   | 6                    |

| Diodes                       | 30                        | -                    | -                    | -                    |

| Capacitors                   | -                         | 21                   | -                    | -                    |

| Pair of coupled<br>inductors | -                         | -                    | -                    | 1                    |

| DC sources                   | 1                         | 1                    | 3                    | 1                    |

Table 2 Comparison of elements of different seven level inverter topologies

# **IV.SIMULATION RESULTS**

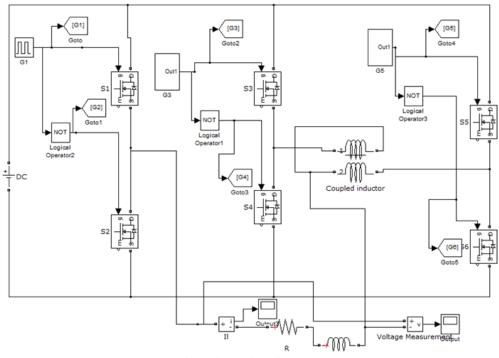

The modified inverter is simulated in MATLAB/Simulink environment. The simulation diagram is shown in Fig 2

Fig.2 Simulation diagram

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 11, November 2015

The simulation parameters are given in Table 3.

Table 3 Simulation Parameters

| Parameters      | Values |

|-----------------|--------|

| Input voltage   | 150V   |

| Load resistance | 33Ω    |

| $L_1$           | 3mH    |

| L <sub>2</sub>  | 12mH   |

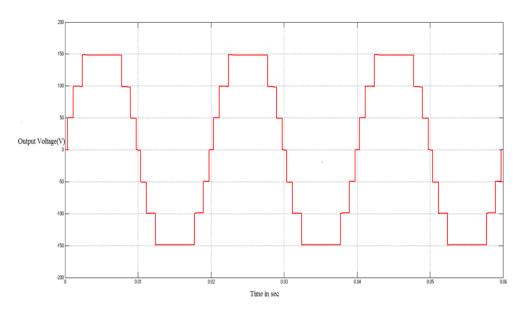

The seven level output voltage is shown in Fig 3

Fig .3Output voltage of the modified inverter

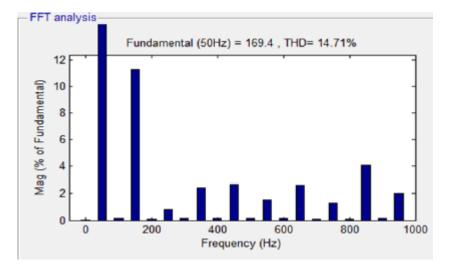

The THD analysis of the modified inverter is shown in Fig 4.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 11, November 2015

Fig 4 FFT analysis of modified inverter

## VI.HARDWARE IMPLEMENTATION

The hardware model of the seven level inverter was developed and the hardware setup is shown in Fig 5.

Fig.5 Hardware setup

Hardware section consists of three parts; control circuit, drive circuit and power circuit. In the control circuit gate signals for the switches are generated according to the logic given in Table I. gate signal. The switching pulses generated using arduino board with an atmel avr processor. Driver circuits are used to boost the gate signal to the required driving voltage of the switches. TLP250 is used to drive the MOSFET. This opt coupler can also provide isolation between the pulse generating unit and power circuit. The power circuit consists of MOSFET IRFP250 and the coupled inductor with mutual inductance of 6mH. The output waveform is taken across the load of 330hm.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 11, November 2015

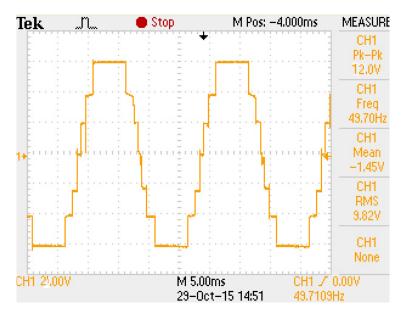

The input given by a 6V battery. A seven level AC voltage with a peak of 6V is obtained as the output. The frequency of the output waveform is 50Hz. The Fig.6 is the obtained output wave form.

Fig.6 Output voltage waveform

The THD of the output waveform is obtained from the harmonic analyser is shown in Fig.7

| VIEW |                     | HAR   | HARMONICS |      | •>•# USB |      | 8 2015/10/14<br>15:52:37 |

|------|---------------------|-------|-----------|------|----------|------|--------------------------|

| SET  |                     | 1P2W  | 1P2W 10A  |      | 230V     |      | 0.00Hz                   |

| 0    | rder                | U [V] | Ι         | [A]  | Ρ        | [₩]  | CH1                      |

|      | 1                   | 4.4   | e         | .13  | 0        | 001k |                          |

|      | 2                   | 0.1   | - 6       | 0.01 | 0.       | 000k | THD1 [%]                 |

|      | - 3                 | 0.5   | - 6       | 1.01 | 0.       | 000k | 13.2                     |

|      | 4                   | 0.1   | - 6       | 1.00 | 0.       | 000k | 13.2                     |

|      | 5                   | 0.1   | - 8       | .01  | 0.       | 000k |                          |

|      | 6                   | 0.0   | - 8       | 1.00 | 0.       | 000k |                          |

|      | 7                   | 0.1   | - 8       | 1.00 | 0.       | 000k |                          |

|      | 8                   | 0.0   | - 8       | 1.00 | 0.       | 000k |                          |

|      | 9                   | 0.1   | - 6       | 1.00 | 0.       | 000k |                          |

|      | 10                  | 0.0   | - 6       | 1.00 | 0.       | 000k |                          |

|      | - 11                | 0.1   | - 6       | 1.00 | 0.       | 000k |                          |

|      | 12                  | 0.0   | - 8       | 1.00 | 0.       | 000k |                          |

|      | 13                  | 0.1   | - 8       | 1.00 | 0.       | 000k |                          |

|      | 14                  | 0.0   | - 6       | 1.00 | 0.       | 000k |                          |

|      | 15                  | 0.0   | - 6       | 1.00 | 0.       | 000k |                          |

|      | 16                  | 0.0   | - 6       | 1.00 | 0.       | 000k |                          |

|      | 17                  | 0.2   | 6         | .00  | 0.       | 000k |                          |

| GR   | GRAP/LIST CH SELECT |       |           |      |          |      | HOLD                     |

Fig.7 THD analysis

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 11, November 2015

## VII.CONCLUSION

This work has presented a topology of multilevel inverters with coupled inductors. The advantages with multilevel inverters over two-level inverters are clear. If low disturbances or low switching power loss is wanted, multilevel inverters are certainly a solution. The modified inverter uses less number of power electronic switches and dc sources than the conventional multilevel inverters. This seven level inverter is suitable for low voltage, low / medium power applications.

#### REFERENCES

- [1] Z. Li, P. Wang, Y. Li, and F. Gao, "A Novel Single-Phase Five-Level Inverter with Coupled Inductors,"IEEE Trans.on Power Electronics, vol. 27, no. 6, pp. 27 16-2726, June 2012.

- [2] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A Survey of topologies, controls, and applications,", IEEE Trans.Ind. Electron., vol. 49, no. 4, pp. 724738, Aug.2002.

- [3] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 22192230, Jul.2010

- [4] M.Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 21972206, Jul.2010

- [5] A. M. Knight, J. Ewanchuk, and J. C. Salmon, "Coupled three-phase inductors for interleaved inverter switching," IEEE Trans. Magn., vol. 44, no. 11, pp. 41994122, Nov.2008

- [6] J. Salmon, A. Knight, and J. Ewanchuk, "Single phase multi-level PWM inverter topologies using coupled inductors," in Proc. IEEE Power Electron. Spec. Conf. (PESC), 2008, pp. 802808