|| Volume 9, Issue 6, June 2020 ||

# A Tiny and Multifunction ICAP Controller for Reconfigurable System Using Zynq 7000 SoC

<sup>1</sup>A.Sanhita. <sup>2</sup>Mr.K.Rakesh

<sup>1</sup>M.Tech Student, Department of ECE, MVGR College of Engineering, Vizianagaram, Andhrapradesh, India <sup>2</sup>Assistant Professor, Department of ECE, MVGR College of Engineering, Vizianagaram, Andhrapradesh, India

ABSTRACT: Dynamic partial reconfiguration is the ability to reconfigure some portions on FPGA during its run time. It offers new plan space with different advantages, lessen the setup time and spare memory as the fractional reconfiguration records are littler than full ones and furthermore diminish the dynamic force utilization spares the assets. The Field Programmable Gate Array (FPGA) chip's innovation permitted equipment configuration being as adaptable as programming and has taken huge spot continuously applications. Improving the asset use of FPGA after some time and space is where the Dynamic halfway reconfiguration methodology is a significant component of FPGA. The utilization of Soft IP's diminishes the structure time and builds the adaptability of FPGA use in which the internal configuration access port (ICAP) controller IP center is a significant piece of reconfiguration framework. ICAP in the static locale takes up a portion of the assets of the reconfiguration framework and lessening the asset control of ICAP controller and accounting for equipment errands execution in reconfigurable zones is significant application. A reconfigurable system is built to test the functionality of ICAP controller and is mapped to a real time application.

Keywords: ICAP controller, Field Programmable Gate Array (FPGA), CPU, UART controller.

## I. INTRODUCTION

Field programmable gate arrays (FPGA), functionality can be changed by configuring it with bit stream and it offers Massive parallelism during its operation. Due to its adaptability, it tends to be adoptable to different applications. Dynamic Partial reconfiguration is the Process of arranging a portion of the chose hinders on FPGA, while the rest of the part proceeds with its activity. i.e., the chose areas on the FPGA will be stacked with new piece streams during run time. This is particularly important where gadgets work in a strategic domain that can't be disturbed while a few subsystems are being reclassified. Its uses can be best utilized in the applications where FPGA should be go about as a smart gadget, to change its response as indicated by the working condition. Halfway reconfiguration is appropriate for plans with numerous stages that don't work at the same time and subsequently can share the assets on FPGA. In such frameworks, one segment of FPGA keeps on working, while other segment is reconfigured with new usefulness. This began from minuscule reconfigurable alterations of a CPU, over complex video preparing and database speeding up to programming characterized radio applications. Basic for every one of these applications is that they profit by having the option to move modules to various positions and to pack different modules together into a common reconfigurable locale. Fractional reconfiguration furnishes the creators with the advantages of diminished gadget check, decreased force and in general decreased expense. At the point when utilized related to the dynamic reconfiguration of handsets, it gives an adaptable answer for actualize high Bandwidth applications.

|| Volume 9, Issue 6, June 2020 ||

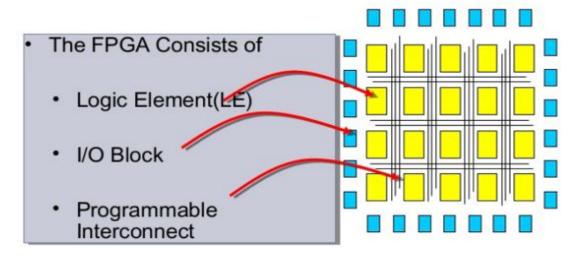

Figure 1: Field programmable Gate Arrays (FPGAs).

Field programmable Gate Arrays (FPGAs) give an intriguing arrangement when custom rationale is required for brief timeframe to showcase items. The items implanting FPGA System on chip arrangements permit them to be refreshed once sent. Late FPGA models, for example, Xilinx Virtex Series, take into account halfway and dynamic run-time reconfiguration. The FPGA texture can adjust its arrangement information at run-time, empowering replacement of explicit segments of an executed equipment configuration making the framework be adjusted to the requirements of the application. Henceforth dependability, disappointment repetition and runtime adaptively by utilization of dynamic halfway reconfiguration are presented that are basic angles for installed frameworks. As the FPGA comprised of multiple modules, few modules, which are to be dynamically reconfigured are clustered leaving the static modules.

# II. LITERATURE REVIEW

Dr. GarimaBandhawarkarWakhle et al. suggested that, the UART is the usage of the consecutive correspondence show, which permits the full duplex correspondence in successive association. They plan the hardware utilization of a quick and prepared UART using Field Programmable Gate Array. The UART contains three sections, specifically beneficiary, transmitter and baud rate generator which is furthermore repeat divider. They duplicated on Modelsim SE 10.0a and plan by using Verilog delineation language which has been consolidated on FPGA units like as Spartan3 and Virtex4. Resulting to separating the comparative examination construe that there is a qualification in the amount of cuts, LUTs and the most extraordinary repeat. The results are extremely consistent and strong and have phenomenal flexibility with high blend. In case we use FIFO in describing the UART our arrangement turns as progressively versatile, consistent and strong which gives most raised bps rate. [12]

Amanpreet Kaur, Amandeep Kaur, describes that A UART is a full duplex location. It is the programmable processor that manages a PC's a back-to - back interface. It includes the connection between incremental and equal results. The entire gradual transmission system works according to the movement select standard. Once the baud rate is initiated, both the transmitter and the collector inside the clock are set to ambiguous rehash during information transmission through the UART. [13]

The build-up of a progressive correspondence with bit synchronization, adjusted baud rate disclosure and transport, rehash divided by clock of information, as demonstrated by Bhavna fertilizer and Rahul residence. Both modules are re-updated on a vernacular and Verilog programming development platform by Xilinx Spartan-3 FPGA. Throughout the issue portion, test the details you get at various frequencies using the screw-free and baudrate era. Until consolidating the entire system, the Baud Rate Generator is linked to UART programme. For situations where the consumer needs to break down to convenience, the purpose of the rehash divider. As shown by need, this recurring division will change regularly. Seen multiple waveforms between 150 bps and 38400 bps at various frequencies at

|| Volume 9, Issue 6, June 2020 ||

50 MHz clock cycles. The re-enacting waveforms demonstrate the accuracy of HDL execution and display the configuration and highlights of the UART layout of the baud rate generator. [14]

Tooth Yi-Yuan Chen Xue-Jun is mindful of the fundamental recipient of the asynchronous Transmitters commonly use low speed, short-run, irrelevant PC-peripheral information for gradual correspondence. In order to transmit accurate, secure and functional details, you can combine the UART composed of a VHDL language with the Field Programmable Gate array. It is necessary for the Machine on Chip game plan. The findings of Quartus II reintroduction are entirely accurate with UART. VHDL acts as a program language for the description of the UART modules in this article. The development and check component is finished by using the Altera Cyclone action FPGA chip programming from Quarter II. The findings are accurate, consistency, strong cohesion of the system, mind blowing adaptability with some reference respect. From a general perspective in electronic sorting out field, where SOC advancement has beginning late wound up being widely utilized, this course of action displays astounding monstrosity. [15]

From the assessment, it is seen that the utilization of UART on an essential level uses the on-chip UART IP extreme as nails since it has unmatched, at any rate it has defenseless adaptability and vulnerable transportability, It is also typically not appropriate to satisfy the customer's strong needs. With the quick advancement of the responsive FPGA base, a high degree of adaptability, transportability and the course of operation is an unavoidable essential activity in the built system, subject to top of the line. Huimei Yuan, Junyou Yang and Pan displayed modern technologies, offering the great UART IP Soft Core architecture based on DMA mode. [16]

Tooth Yi-Yuan CHEN XUE-Jun addressed the paper on the design and reproduction of the successive VHDL contact element. They presented in this article the UART as the programmed microchip that scans a PC's peripherals interface. It is known to be the most widely utilized incremental circuit of information. The entire methodology of incremental dissemination would rely on the movement enrollment pattern. There are two primary forms of synchronous and asynchronous back to back communication. In synchronous continuous correspondence, the sender and the receiver will fire at an estimated time. Abnormal transmission involves the transmission of information to the finder without sending a clock pennant. This system utilizes VHDL as the vernacular course of operation for the UART units. The findings are good and reliable. The design has a clear relation and remarkable adaptability with a certain reverence for references [17].

A paper was presented by Shouqian Yu, Lily Yi, Wihai Chen, Zhao Jin Wen on the implementation of the FIFO Technique and FPGA multichannel UART controller. In this article they have demonstrated that FIFO is used for complete correspondence between fast contraction and low speed equipment or complete correspondence between a comparative subcontroller within a couple of structures such as the high data combination system, fast control under PCI and multi DSP signal ready system. FIFO is the most critical component of such systems which may be seen as a mechanism between multiple contraptions. In fact, the odd FIFO connected to FPGA is the main component of our control scheme. Around the same moment. Therefore, our planner picks characteristics and boundaries of the non-concurring FIFO. FIFO can be used in the identical or comparable port to full correspondence [18].

#### III. DESIGN ON FPGA

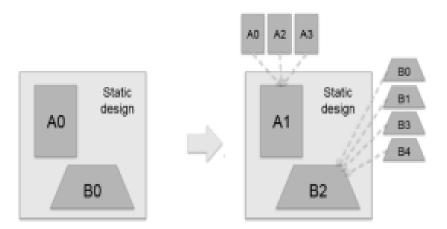

Its design is implemented as modules, in partial reconfiguration some of the selected modules are reconfigured, while in full reconfiguration all the modules need to be reconfigured but this takes more time to reconfigure and more power consumption compared to partial reconfiguration. It needs more number of bit streams to be loaded and cost also increases. Below diagram shows the difference between partial and fully reconfigured system's in terms of bit stream files, it is obvious that number of bit stream files to fully reconfigure are more than the partial reconfiguration.

|| Volume 9, Issue 6, June 2020 ||

Figure 2: Difference between full and partial reconfiguration.

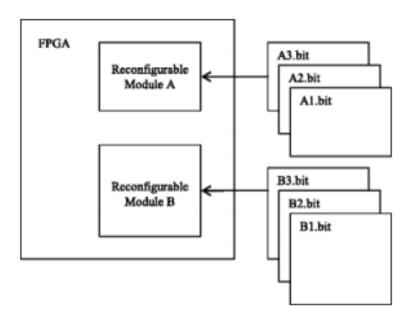

Below diagram shows the reconfigurable modules A and B leaving the static modules, these reconfigurable modules will have multiple bit stream files, based on the application requirement appropriate file will be configured into the module.

Figure 3: Multiple bit streams of Reconfigurable module

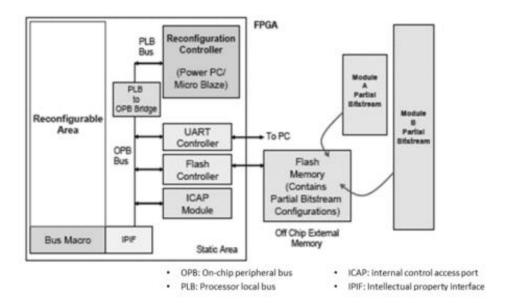

Below diagram shows the block level implementation of Partial reconfiguration, the framework is associated with an outside Flash memory by means of a Flash controller which gives read/compose access to the outer memory. The ICAP module is available to peruse/compose design information to/from the gadgets' setup memory. Reconfiguration of the dynamic area is overseen by a Reconfiguration Controller which can be either outer or inside (self-setup) to the FPGA.

#### || Volume 9, Issue 6, June 2020 ||

Figure 4: Block diagram of Dynamic Partial reconfiguration

It is liable for the fractional reconfiguration bit stream that must be stacked onto the reconfigurable particular district. Be that as it may, self-setup can be helped out through the interior ICAP equal interface and lessens reconfiguration time when contrasted with outer reconfiguration. Thus, our reconfiguration controller is available inside the FPGA and imparts to the remainder of the framework by means of the Processor Local Bus (PLB).

## IV. PROBLEM DEFINITION

- When the UART transmitter finishes the transmission and the transmission buffer is zero, the "Underrun Malfunction" occurs. For non-competitive modes, this is viewed as an indicator that no information remains to be transmitted, because additional stop bits may be applied to the results. This mistaken sign is popular in USART's as an underrun in parallel systems is increasingly real.

- If it does not see a "stop" bit at a standard "stop" bit moment, UART can recognize a nearby fault. Since the "start" bit is used to distinguish the beginning of an approaching event, its preparation is a guideline for the other pieces. If the information line does not appear in regular condition, the UART would signal a confining blunder while the "stop" bit is usual (as per the sum of knowledge or bits of equality on which the UART is set). An encircling error is often a "split" state on the rows.

- Equality mistake occurs when one-bit equality cannot help contradicting the equality bit predefined. Having an equality bit is arbitrary, and if equality tests are enabled, this error can occur.

- A break condition occurs if the beneficiary information is at the 'space' level for a longer period of time, usually for more than one character time (rational low, i.e. '0'). This isn't exactly a failure, but it seems that every zerobit has a corresponding fault for the receiver. The term "split" comes from the flagging circles used by teletypewriters as the standard flagging. No current streaming indicates the "dispersion" status of the existing circle line and a daily split or some fault in the line triggers an unusually significant volume of no existing streaming.

|| Volume 9, Issue 6, June 2020 ||

#### V. PROPOSED METHODOLOGY

## A. Eradication coding based sending Algorithm

The sending measurement based on eradication coding may be understood to boost the measurement of simple replication. A method of direct duplication where indiscriminate copies of the message are transmitted through the r contacts concept. Here, r is the factor of replication. Just send different copies of the message. You can only transmit the hand-off center points to the objective; you cannot propel it to another hand-off. It creates a low overhead because the flooding of the message is regulated by the source. For both instances, the two-hop step count is this type of sending statistics. Trademark competition occurs between overhead (r) and inactivity of data transfer. A higher r allows smaller gaps to accumulate / transmissions.

In accordance with replication factor r, vagueness copies of r communications are submitted from the source and gestures will clearly be sent authentically to the target. At first we encrypt the message at the root in the count dependent on destruction and create a large amount of code squares. For a certain trustworthy k, the coded squares are also divided into main k movements. In this stage, it uses a factor of k more exchanges and a factor of k less data is exchanged through more hand-off. The sum of bytes transmitted is k in each event, commensurate with the volume of bytes distributed by srep k. The message can be decoded before and after the cancelation code has been used (with k, message size k), when k of the generated code squares is provided. The message will be decoded as some k moves pass the data on, as code squares are spread between k moves, if we assume that no code squares would be lost during transfers to and from a handout. Just where k has a similar influence on the extinction coding method because the simple duplication solution is to use the standard k motions and a duplicate of each k document.

#### B. Favorable circumstances of eradication coding in sending

Motions are used to enhance the implementation of the concession in the necessary replication. Instead, the erasure coding technique utilizes kr gestures for a comparable overhead. Thus, one can expect that the chances of a few movements with low delays are higher than those with just r movements are different. Simultaneously, cancelation coding involves some good k movements (unlike 1 Srep) in order to repeat the results. And if the number of these small concession gestures is greater than k, the theory of erasure coding effectively transmits the message less rapidly than direct reproduction. The basic assumption is that if k is enormous, the distribution of the awarded is clear. Therefore, a constant deferment can be ensured with the cancelation coding philosophy.

### VI. RESULT ANALYSIS

We have recreated every single piece of our module independently in ZYNQ 7000 SoC. The recreation results for the 'baudgen', 'fifo', 'uartrx', and 'uart-tx' sub modules are appeared in the figures beneath individually. We have blend top module in Xilinxvivado 18.2.

## A. Testing

Our center in Xilinxvivado 18.2 starter unit. The test circuit has an enlarged that takes one parellel data set aside in The all out focus was similarly attempted by interfacing it with the PC by a RS232 connect in the wake of executing a test circuit joining the rx-fifo ensuing to getting got by the UART module, builds it by one and a short time later gives it back to the tx-fifo which is then transmitted successively by the module the examining from the fifo, incrementation and staying in contact with the fifo is done each character thusly when a switch(connected with the test circuit through adebouncer regardless different eading and making out of NULL-character could convey inaccurate result) is pressed. Here we recently created in 4 characters(displayed locally in the helper terminal window) which are taken care of in the fifo, by then crushed the allotted switch on numerous occasions which eturns the set aside characters expanded by one and are demonstrated again in the hyperterminal (as showed up in Figure 5)

|| Volume 9, Issue 6, June 2020 ||

#### B. Territory and Power

All out level of the gadget assets used to execute our module has been determined by Xilinxvivado 18.2 synthesizer which is seen as ostensible.

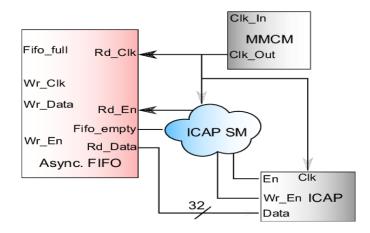

Figure 5: Block Diagram of ICAP controller.

In the above figure 5 the model if ICAP controller has been shown.

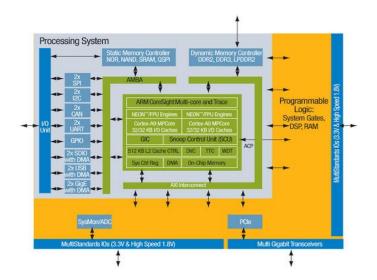

Figure 6: Implementation model of ZYNQ 7000 SoC.

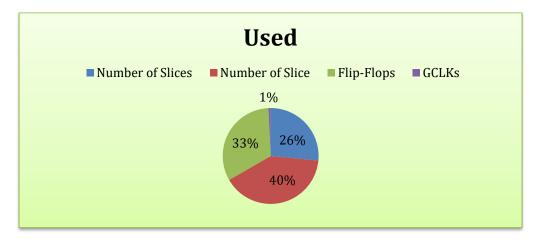

Table 1: Comparison analysis of available sources along with utilization.

| Logic Utilization | Used | Available | Utilization |

|-------------------|------|-----------|-------------|

| Number of Slices  | 35   | 465       | 4.3%        |

| Number of Slice   | 53   | 931       | 3.78%       |

| Flip-Flops        | 43   | 932       | 8.89%       |

| GCLKs             | 1    | 244       | 2.43%       |

|| Volume 9, Issue 6, June 2020 ||

The table above 1 explains about the Number of Slice, Number of Slice Flip-Flops, Number of GCLKs comparisons has been shown.

Figure 7: Estimated values representation.

The above figure 7 represents the estimated values according to the resources available and used.

#### VII. CONCLUSION

It is possible to use run time partial reconfiguration to save both power and area, an intelligent run time system is needed to ensure that power is saved and that timing constraints are meet, when using in real time systems. Measuring power consumed during partial reconfiguration aids in determining the design of the run time system and the feasibility of using dynamic partial reconfiguration.

#### REFERENCES

- [1]. W. Guohua, L. Dongming, W. Fengzhou, A. Adetomi and T. Arslan, "A tiny and multifunctional ICAP controller for dynamic partial reconfiguration system," 2017 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Pasadena, CA, 2017.

- [2]. S. Wang and X. Huang, "Implementation of Partial Reconfiguration Based on FPGA," 2018 2nd IEEE Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), Xi'an. 2018.

- [3]. https://ieeexplore.ieee.org/document/7983723.

- [4]. FANG Yi-Yuan CHEN Xue-Jun, Design and Simulation of UART Serial Communication Module Based on VHDL Shanghai University of Engineering Science, 2011"

- [5]. Amanpreet Kaur, Amandeep Kaur, "An approach for designing a universal asynchronous receiver transmitter (UART)", International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, Issue 3, May-Jun 2012, pp.2305-2311.

- [6]. "3.en.wikipedia.org/wiki/synchronous serial communication."

- [7]. "Cowley, John (2007) communication and networking, An introduction, Springer, ISBN 9781846286452."

- [8]. "www.pccompi.com"

- [9]. "Shiva, S.G University of Alabama in Huntsville, AL, proceedings of the IEEE (volume 67, Issue: 12)."

- [10]. "Comparison of VHDL, Verilog and System Verilog, by StephenBailey, www.model.com"

- [11]. C. H. Roth, "Digital System Design Using VHDL", PWSPublishing Company, 2008.

- [12]. Dr. Garima Bandhawarkar Wakhle, Iti Aggarwal and Shweta Gaba," Synthesis and Implementation of UART using VHDL Codes", International Symposium on Computer, Consumer and Control, 978-0-7695-4655-1/12© 2012 IEEE DOI 10.1109/IS3C.2012.10.

- [13]. Amanpreet Kaur, Amandeep Kaur, "An Approach For Designing A Universal Asynchronous Receiver Transmitter (UART)", IJERA Vol. 2, Issue 3, May-Jun 2012, pp.

- [14]. "Bhavna manure and Rahul tanwar, UART with automatic baud rate generator and frequency divider Journal of Information Systems and Communication on 15feb 2012."

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (IJAREEIE)

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

## || Volume 9, Issue 6, June 2020 ||

- [15]. "FANG Yi-Yuan CHEN Xue-Jun, Design and Simulation of UART Serial Communication Module Based on VHDL, IEEE JOURNAL in 2011."

- [16]. "Huimei Yuan, Junyou Yang, Peipei Pan, Optimized Design of UART IP Soft Core based on DMA Mode978-1-4244-5046-6/10 2010 IEEE."

- [17]. "FANG Yi-Yuan CHEN XUE- Jun, Design and simulation Of UART serial communication Module Based on VHDL, 2011."

- [18]. "Shouqian Yu ,Lili Yi, Weihai Chen, Zhao jin Wen, Implementation of a Multi-channel UART Controller Based on FIFO Technique and FPGA 2007."