(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijareeie.com</u> Vol. 6, Issue 3, March 2017

# Address Generator For WiMAX Deinterleaver with Optimized Multiplier Design

### Abin Jacob<sup>1</sup>, Jinto Mathew<sup>2</sup>

PG Student [ACIS], Dept. of ECE, Mar Baseliose Institute of Technology and Science, Nellimattom, Kerala, India<sup>1</sup>

Assistant Professor, Dept. of ECE, Mar Baseliose Institute of Technology and Science, Nellimattom, Kerala, India<sup>2</sup>

**ABSTRACT**: In this brief, a low-complexity and novel techniques proposed to efficiently implement the address generation circuitry of the 2-D deinterleaver used in the WiMAX transreceiver using the Xilinx field-programmable gate array (FPGA). The floor function associated with the implementation of the steps, required for the permutation of the incoming bit stream in channel interleaver/deinterleaver for IEEE 802.16e standard is very difficult to implement in FPGA. A simple algorithm along with its mathematical background developed in this brief, eliminates the requirement of floor function and thereby allows low-complexity FPGA implementation. The use of an internal multiplier of FPGA and the sharing of resources for quadrature phase-shift keying, 16-quadrature-amplitude modulation (QAM), and 64-QAM modulations along with all possible code rates makes our approach to be novel and highly efficient when compared with conventional look-up table-based approach. The proposed approach exhibits significant improvement in the use of FPGA resources and Design of a customized multiplier which give more efficient and less complex system. Exhaustive simulation has been carried out to claim supremacy of our proposed work.

### KEYWORDS: WIMAX, DE-INTERLEAVER, FPGA, QAM

### I. INTRODUCTION

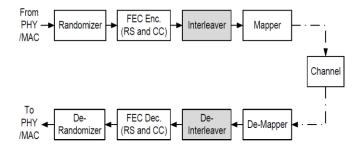

BROADBAND wireless access (BWA) is continuously becoming a more challenging competitor to the conventional wired last mile access technologies [1]. IEEE has developed standards for mobile BWA (IEEE 802.16e) popularly referred to as mobile WiMAX [2]. The channel interleaver employed in the WiMAXt transceiver plays a vital role in minimizing the effect of burst error. In this brief, a novel, low-complexity, high-speed, and resource-efficient address generator for the channel deinterleaver used in the WiMAX transreceiver eliminating the requirement of floor function is proposed. SILICON COST of the permutation tables for interleaver implementation used in the conventional approaches can be very high if the device is supporting many variants inside a particular standard. Low cost on-the-fly address computation with supporting multiple variants has been a challenge due to presence of complex functions. Therefore a low cost and re-configurable architecture for address computation is always beneficial. WiMAX is being used in the communication industry with many variants in channel coding, like different block sizes and different modulation schemes (e.g. BPSK, QPSK, 16- QAM and 64-QAM). System level overview for WiMAX showing use of channel interleaver is shown in Fig. 1. The type of interleaver used here is the block interleaver.

Fig 1: Overview of encoding in WiMAX channel

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijareeie.com</u>

### Vol. 6, Issue 3, March 2017

The block interleaver can also be considered as a row-column matrix. In this case, data is written row-wise in a memory configured as a row-column matrix and then read column wise after applying certain intra-row and inter-row permutations. Very few works related to hardware implementation of the interleaver/deinterleaver used in a WiMAX system is available in the literature. The work in [3] demonstrates the grouping of incoming data streams into the block to reduce the frequency of memory access in a deinterleaver using a conventional look-up table (LUT)- based CMOS address generator for WiMAX. Khater et al. [4] has described a hardware description language (VHDL)- based implementation of address generator for IEEE 802.16e channel interleaver with only a 1/2 code rate. In [5], the authors have described a finite-state machine (FSM)-based address generator of the same interleaver for all permissible code rates and modulation schemes. Both [4] and [5] are tested on the field-programmable gate array (FPGA) platform. Asghar and Liu in [6] has made 2-D translation of the functions used in WiMAX channel deinterleaver to claim efficient hardware architecture. However, the derivations in [6] do not clearly explain the design issues, particularly for 64-quadrature-amplitude modulation (QAM). Hardware implementation of floor function is very complex and consumes abnormally large amount of resources [6]. Conventional LUT-based technique is found to be unattractive from many aspects such as slowness in operation, consumption of large logic resources leading to inefficiency in resource utilization, etc. A comparative study with a LUT-based technique confirms the superiority of our proposed design. As compared with the complicated and lengthy expressions, particularly for 16-QAM and 64-QAM, due to the 2-D translation in [6], a compact and user-friendly mathematical representation and subsequent algorithm is proposed. The mathematical expressions have formally been proven using [6]. Our proposed algorithm when realized by digital hardware results in low-complexity architecture for the address generator compared with prevailing technique. The basic objective and significance of this project are,

#### Objective

- To eliminate the conventional LUT method to improve the system.

- To study the WiMAXinterleaver and deinterleaver concepts.

- To study the implementation and improvisation of the existing equation to more simple form.

- To evaluate the issue that facing while practical implementation.

- To provides performance improvement by reducing interconnection delay, efficient resource utilization, and lesser power consumption due to the conventional multipliers.

#### Significance

- In previous study, derivations in 2D realization do not clearly explain the design issues, particularly for 64quadrature-amplitude modulation (QAM); which made issues in practical implementation.

- Conventional LUT-based technique is found to be unattractive from many aspects such as slowness in operation, consumption of large logic resources leading to inefficiency in resource utilization.

- Previous study carries complicated and lengthy expressions, particularly for 16-QAM and 64-QAM, due to the 2-D translation.

- Any of the previous study not includes the multiplier designing factors which affects speed, resource utilization, and power consumption.

#### **II. BASIC ALGORITHM**

#### Interleaving Wimax

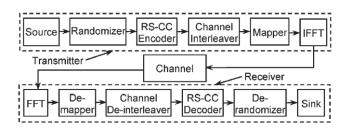

Fig 2: Block diagram of the WiMAX trans-receiver.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 3, March 2017

The mandatory blocks of a WiMAX transreceiver are shown in Fig.2. Data stream received from a source is randomized before being encoded by two forward error correction (FEC) coding techniques, namely, Reed–Solomon (RS) and convolutional coding (CC). The channel interleaver permutes the encoded bit stream to reduce the effect of burst error. When convolutional turbo code (CTC) is used for FEC, being optional in WiMAX, the channel interleaver is not required, since CTC itself includes an interleaver within it [7]. Modulation and construction of orthogonal frequency-division multiplexing symbols are performed by the two subsequent blocks, namely, mapper and inverse fast Fourier transform of Fig.4.1. In the receiver, the blocks are organized in the reverse order enabling the restoration of the original data sequence at the output.

Fig 3: Block diagram of interleaver/deinterleaver structure.

Two-dimensional block interleaver/deinterleaver structure, which is used as a channel interleaver/deinterleaver in the WiMAX system, is described in Fig.4.2. It has two memory blocks, namely, M-1/2 and an address generator. In block interleaving, when one memory block is being written, the other one is read, and vice versa. When sel = 1, write-enabled signal WE of M-1 is active. During this period, the input data stream is written in M-1 as it receives the write addresses. Simultaneously, an interleaved data stream is read from M-2 as it is supplied with the read addresses. After the memory blocks are written/read up to the desired location as specified by interleaver depth, the status of sel signal is changed to swap the read/write operation.

### PROPOSED ALGORITHM

Here, the proposed algorithm for address generator of the WiMAXdeinterleaver along with its mathematical background has been described.

| <i>N<sub>cbps</sub></i> , code rate and modulation type |    | De-inter | rleaver a | ddresse | s  |

|---------------------------------------------------------|----|----------|-----------|---------|----|

|                                                         | 0  | 16       | 32        | 48      | 64 |

| N <sub>cbps</sub> = 96-bits, ½<br>code rate,            | 1  | 17       | 33        | 49      | 65 |

| QPSK                                                    | 2  | 18       | 34        | 50      | 66 |

| QI SIX                                                  | 3  | 19       | 35        | 51      | 67 |

| AL 400 hits                                             | 0  | 16       | 32        | 48      | 64 |

| N <sub>cbps</sub> = 192-bits,<br>½ code rate,           | 17 | 1        | 49        | 33      | 81 |

| 72 CODE Tale,<br>16-QAM                                 | 2  | 18       | 34        | 50      | 66 |

| 10-0211                                                 | 19 | 3        | 51        | 35      | 83 |

|                                                         | 0  | 16       | 32        | 48      | 64 |

| $N_{cbps} = 576$ -bits, $\frac{3}{4}$                   | 17 | 33       | 1         | 65      | 81 |

| code rate,<br>64-QAM                                    | 34 | 2        | 18        | 82      | 50 |

| 04-QAIVI                                                | 3  | 19       | 35        | 51      | 67 |

TABLE 4: First four rows and five columns of deinterleaver sample addresses

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 3, March 2017

| Row<br>no.(j) | Column<br>no. (i) →     | 0        | 1        | 2        | 3        | 4        |

|---------------|-------------------------|----------|----------|----------|----------|----------|

| 0             | N <sub>cbps</sub> = 96- | d.0+0=0  | d.1+0=16 | d.2+0=32 | d.3+0=48 | d.4+0=64 |

| 1             | bits, 1/2               | d.0+1=1  | d.1+1=17 | d.2+1=33 | d.3+1=49 | d.4+1=65 |

| 2             | code rate,              | d.0+2=2  | d.1+2=18 | d.2+2=34 | d.3+2=50 | d.4+2=66 |

| 3             | QPSK                    | d.0+3=3  | d.1+3=19 | d.2+3=35 | d.3+3=51 | d.4+3=67 |

| 0             | N <sub>cbps</sub> =     | d.0+0=0  | d.1+0=16 | d.2+0=32 | d.3+0=48 | d.4+0=64 |

| 1             | 192-bits,<br>½ code     | d.1+1=17 | d.0+1=1  | d.3+1=49 | d.2+1=33 | d.5+1=81 |

| 2             | rate,                   | d.0+2=2  | d.1+2=18 | d.2+2=34 | d.3+2=50 | d.4+2=66 |

| 3             | 16-QAM                  | d.1+3=19 | d.0+3=3  | d.3+3=51 | d.2+3=35 | d.5+3=83 |

TABLE 5: Determination of correlation between addresses

Table 4 shows the deinterleaver addresses for the first four rows and five columns of each modulation type. As d = 16 is chosen, the number of rows are fixed (= d) for all Ncbps, whereas the number of columns are given by Ncbps/d. A close examination of the addresses in Table 4.1 reveals that the correlation between them follows the manner, as shown in Table 5. The mathematical foundation of the correlation between the addresses, as derived in this brief, is represented by (5)–(6), i.e.,

$$k_{n,\text{QPSK}} = \{ d * i + j \quad \text{for } \forall j \text{ and } \forall i$$

$$k_{n,\text{16-QAM}} = \begin{cases} d * i + j \quad \text{for } j\%2 = 0 \text{ and for } \forall i \\ d * (i + 1) + j \quad \text{for } j\%2 = 1 \text{ and} \\ & \text{for } i\%2 = 0 \\ d * (i - 1) + j \quad \text{for } j\%2 = 1 \text{ and} \\ & \text{for } i\%2 = 1 \end{cases}$$

(5)

From Table 5 and the mathematical representation by (5)–(6), following three algorithms for the three modulation schemes are proposed. These algorithms eliminate the requirement of floor function while generating write addresses. These algorithms are also tested on Modelsim.

A. QPSK

initialize Ncbps and d for j = 0 to d - 1, j + +for i = 0 to (Ncbps/d) - 1, i + +kn = d \*i + jend for end for

B. 16-QAM

initialize Ncbps and d for j = 0 to d - 1, j + +for i = 0 to (Ncbps/d) - 1, i + +if ( $j \mod 2 = 0$ ) kn = d \*i + jelse if ( $i \mod 2 = 0$ ) kn = d \*(i + 1) + jelse kn = d \*(i - 1) + j

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijareeie.com</u> Vol. 6, Issue 3, March 2017

end if end if end for end for

#### **III. DESIGN AND SIMULATION**

#### TRANSFORMATION INTO CIRCUIT

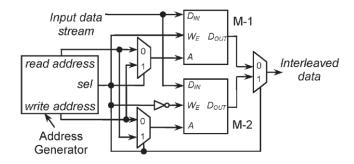

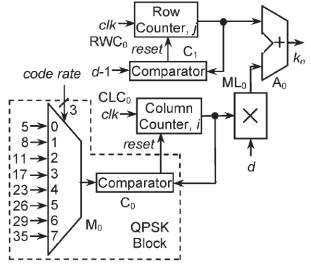

In order to test the proposed algorithms for the address generator of the WiMAXdeinterleaver with all modulation schemes, transformations of these algorithms into digital circuits are made and are shown in Fig.6-7.

Fig 6: Hardware structure of the address generator for QPSK.

The QPSK hardware shown in Fig.6 has a row counter RWC0 to generate row numbers between 0 and d - 1. A column counter CLC0 with multiplexer M0 and comparator C0 generate the variable column numbers to implement permissible Ncbps. A multiplier ML0 and an adder A0 perform the desired operations to implement (5).

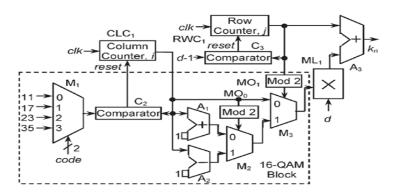

Fig 7: Hardware structure of the address generator for 16-QAM.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 3, March 2017

The address generator for 16-QAM follows a similar structure, such as that of QPSK with few additional modules. These modules are designed with an incrementer, a decrementer, two modulo-2 blocks, and two multiplexers, as shown in Fig.7.

### **IV.SIMULATION RESULT**

The proposed hardware of the address generator is converted into a VHDL program and Simulation results are obtained for all permissible modulation types and code rates using ModelSim SE-64 has been presented in Fig. 8

| 🍫 •             | Msgs     | 3        |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

|-----------------|----------|----------|----|----|----|----|---|----|----|----|----|----|---|----|----|----|-----|

| ᄼ /qpsk/CLK     | 1        |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    | کک) |

| 🖕 /qpsk/RST     |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🛃 /qpsk/CRATE   | 000      | 000      |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🖅 🕹 /qpsk/WADRS |          | 16       | 32 | 48 | 64 | 80 | 1 | 17 | 33 | 49 | 65 | 81 | 2 | 18 | 34 | 50 | 56  |

| 🖅 🔶 /qpsk/cr1   | 00000000 | 0000000  |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| ₽-♦ /qpsk/cr2   | 0000000  | 00000000 |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🖅 🔶 /qpsk/cr3   | 00000000 | 0000000  |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🖅 🔶 /qpsk/M0    | 00000101 | 00000101 |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🔶 /qpsk/CRST    |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 🔶 /qpsk/RRST    |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| ₽-♦ /qpsk/i_ant |          | 1        | 2  | 3  | 4  | 5  | 0 | 1  | 2  | 3  | 4  | 5  | 0 | 1  | 2  | 3  | 4   |

|                 | 0        | 0        |    |    |    |    | 1 |    |    |    |    |    | 2 |    |    |    |     |

| 🖅 - 🔶 /qpsk/d1  | 00001111 | 00001111 |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

| 💽 - 🔶 /qpsk/d   | 00010000 | 00010000 |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

|                 |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

|                 |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

|                 |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

|                 |          |          |    |    |    |    |   |    |    |    |    |    |   |    |    |    |     |

Fig 8: Simulation output for QPSK.

| <b>å</b> .                | Msgs |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

|---------------------------|------|----------|--------|----|-----|-----------|-----|-------|-----|-------|-----|-------|-----|--------|-----|--------|-----|-----|-----|--------|-----|-------|-----|--------|-----|--------|-----|--------|-----|-----|

| 🚸 /qam 16/CLK             | -No  |          |        |    |     | $\square$ |     |       |     |       | n.  |       | h   | Л      |     |        | h   |     | h   | n.     |     |       | n.  | n.     | h   |        | h   | Л      |     | Л   |

| 紣 /qam 16/RST             | -No  |          |        |    |     |           |     |       |     |       | n   |       | h   | Л      |     |        | h   |     | h   | Л      | n   |       | n.  |        | h   |        | h   | Л      |     | Л   |

| 🖅 🎝 /qam 16/CRATE         | -No  | 000      |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| 🖅 🛧 /qam 16/WADRS         | -No  | 16 32    | 48     | 64 | 80  | 96        | 112 | 128   | 144 | 160   | 176 | 17    | 1   | 49     | 33  | 81     | 65  | 113 | 97  | 145    | 129 | 177   | 161 | 2      | 18  | 34     | 50  | 66     | 82  | 98  |

| 🛨 🔶 /qam16/M1             | -No  | 00001011 |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| 🔢 🕁 /qam 16/M2            | -No  | 000)000  | . 000. |    | 000 | . 000     | 000 | . 000 | 000 | . 000 | 000 | . 000 | 000 | . )000 | 000 | . ,000 | 000 | 000 | 000 | . )000 | 000 | . 000 | 000 | . (000 | 000 | . )000 | 000 | . 1000 | 000 | 000 |

| 🔷 /qam16/CRST             | -No  |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| 🔶 /qam 16/RRST            | -No  |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| . <b></b>                 | -No  | 1 2      | 3      | 4  | 5   | 6         | 7   | 8     | 9   | ,10   | 11  | 0     | 1   | 2      | 3   | 4      | 5   | 6   | 7   | 8      | 9   | 10    | 11  | 0      | 1   | 2      | 3   | 4      | 5   | 6   |

| . <b>.</b> � /qam16/j_cnt | -No  | 0        |        |    |     |           |     |       |     |       |     | 1     |     |        |     |        |     |     |     |        |     |       |     | 2      |     |        |     |        |     |     |

| 🖅                         | -No  | 00001111 |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| 🖅                         | -No  | 00010000 |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

| ,                         |      |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

|                           |      |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

|                           |      |          |        |    |     |           |     |       |     |       |     |       |     |        |     |        |     |     |     |        |     |       |     |        |     |        |     |        |     |     |

Fig 9: Simulation output for 16-QAM.

### V. RESULT AND DISCUSSION

A detailed literature survey was done on related topics has proposed a novel algorithm along with its mathematical formulation, including proof for address generation circuitry of the WiMAX channel deinterleaver supporting all possible code rates for modulation patterns QPSK and 16-QAM as per IEEE 802.16e.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 3, March 2017

So the further progression of my work includes 64-QAM and optimized Multiplier design to provide performance improvement by reducing interconnection delay, efficient resource utilization, and lesser power consumption. Also carry implementation and analysis of the same.

#### REFERENCES

- [1] **W. Konhauser**, "*Broadband wireless access solutions—Progressive challenges and potential value of next generation*," Wireless Pers. Commun., vol. 37, no. 3/4, pp. 243–259, May 2006.

- [2] B. Li, Y. Qin, C. P. Low, and C. L. Gwee, "A survey on mobile WiMAX," IEEE Commun. Mag., vol. 45, no. 12, pp. 70–75, Dec. 2007.

- [3] Y. N. Chang and Y. C. Ding, "A low-cost dual mode de-interleaver design," in Proc Int. Conf. Consum. Electron., 2007, pp. 1–2.

- [4] A. A. Khater, M. M. Khairy, and S. E.-D.Habib, "Efficient FPGA implementation for the IEEE 802.16e interleaver," in Proc. Int.Conf. Microelectron., Marrakech, Morocco, 2009, pp. 181–184.

- [5] **R. Asghar and D. Liu**, "2D realization of WiMAX channel interleaver for efficient hardware implementation," in Proc. World Acad. Sci. Eng. Technol., Hong Kong, 2009, vol. 51, pp. 25–29.

- [6] B. K. Upadhyaya, I. S. Misra, and S. K. Sanyal, "Novel design of address generator for WiMAX multimode interleaver using FPGA based finite state machine," in Proc. 13th Int. Conf. Comput. Inf. Technol., Dhaka, Bangladesh, 2010, pp. 153–158.

- [7] **B. K. Upadhyaya and S. K. Sanyal**, *"FPGA Implementation of Address Generator for WiMAXDeinterleaver"*, IEEE transactions on circuits and systems—II: Express Briefs, VOL. 60, NO. 8, AUGUST 2013